# Visualization of a True Random Number Generator

#### **Project 7: Xiphera**

Matti Jämsen, Virpi Sumu 20.8.2021

## **Team members**

#### Matti Jämsen

2nd year Electrical Engineering

#### Virpi Sumu

1st year Automation with a background in Computer Science

#### Xiphera Oy

- Matti Tommiska, CEO

- Valtteri Marttila, developer

# **Project topic**

Xiphera needs a way of demonstrating the advantages their products offer in an easily understandable, visual way to a wider audience, for example at trade fairs and exhibitions.

Xiphera has an IP block for generating true, robust random numbers. The project aims to visualize the advantages of their IP block when compared to generic pseudo random number generators.

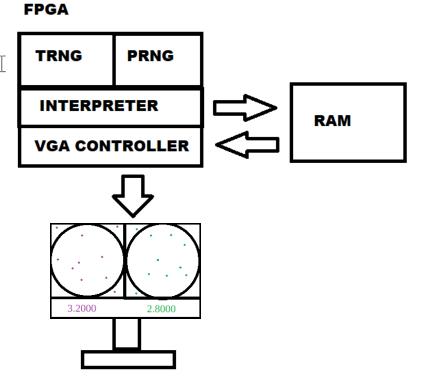

# **Project components**

#### The main components of the project are

- Handling the Xiphera XIP8001B IP block in Intel 10 LP FPGA Ev. kit

- Pseudo random number generator, implemented with a linear feedback shift register to compare deterministic properties with TRNG

- Converting random bit vectors to integer coordinates within a unit circle

- Storage of visualization parameters in RAM

- Output to screen using the VGA standard

- Additionally, the project includes the physical components

- VGA-PMOD connector

- Handheld screen

## **Project components**

#### Process

- Learning the basics

- Hardware description languages (VHDL, Verilog)

- FPGA (Field Programmable Gate Array)

- Cryptography (random number properties and generation)

- Hardware design mindset not consecutive, but concurrent

- VGA standard & connector, testing with Arduino

- All final designs in VHDL

- Appropriately testbenched

- ...modelling the physical components still to be completed

# **VHDL learning curve**

```

library ieee;

use ieee.std logic 1164.all;

use ieee.numeric std.all;

entity ex01 structure is

port(r0, r1, clk : in bit;

q0, q1, : out bit);

end entity;

architecture struct of ex01 structure is

constant limit : integer := 255;

11

signal int clk : bit;

13

begin

storage : process is

variable st r0, st r1 : bit;

15

begin

wait until clk;

17

end process;

end architecture;

Aalto-yliopisto

Sähkötekniikan

korkeakoulu

```

```

library ieee;

use ieee.std logic 1164.all;

entity lfsr 16 tb is

4

architecture arch of lfsr 16 tb is

port (

clk, rst : in std logic;

starter : in std logic vector;

: out std logic vector(31 downto 0);

res

: in std logic;

rd

14

empty

D;

signal clk s, rst s, rd s, empty s : std logic;

signal starter s : std logic vector(15 downto 0) := x"1234";

signal res s

: std logic vector(31 downto 0) := x"00000000";

dut: lfsr port map (clk s, rst s, starter s, res s, rd s, empty s);

clk proc: process

clk s <= '1';

wait for 10 ns;

clk s <= '0';

wait for 10 ns;

end process;

update: process

variable result : std logic vector(31 downto 0) := x"00000000";

```

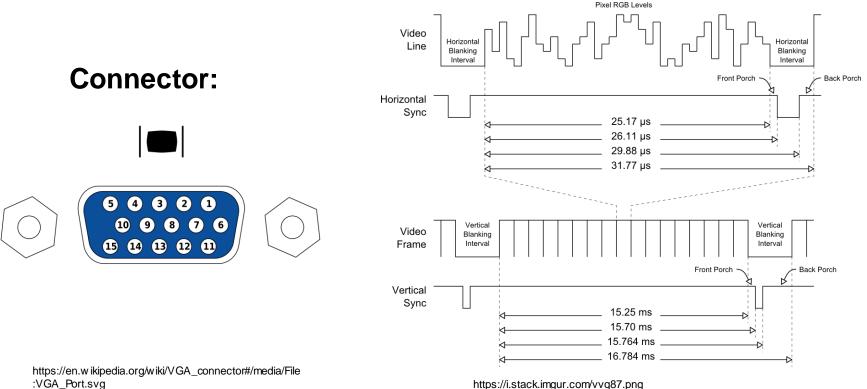

## VGA standard & connector

:VGA\_Port.svg

Aalto-yliopisto Sähkötekniikan korkeakoulu

# VGA standard & connector

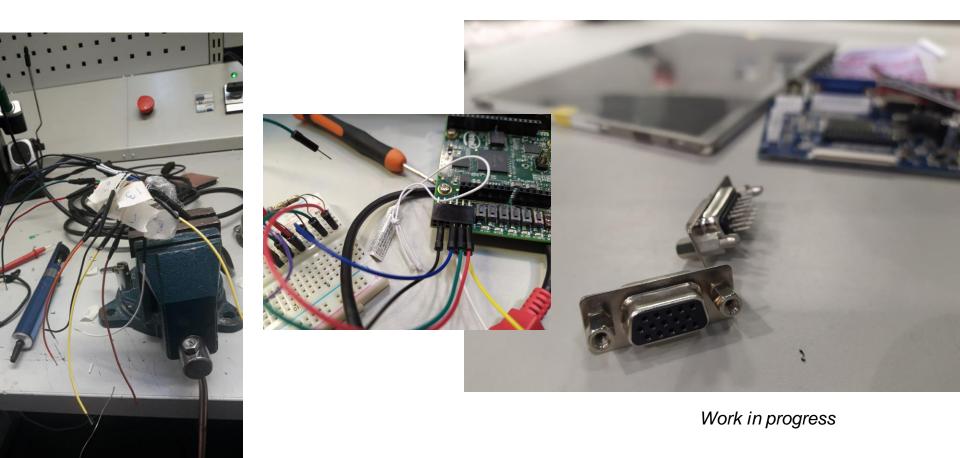

Working connector prototype

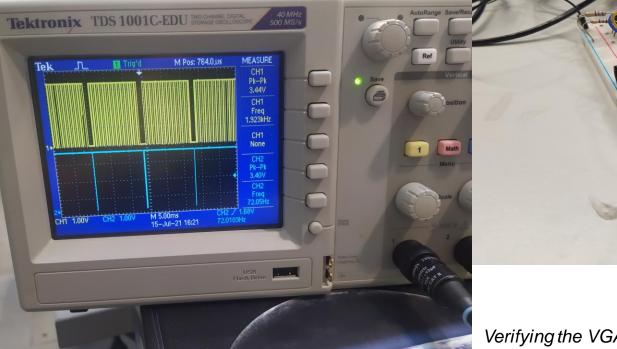

Verifying the VGA signal

### Visualization

## Visualization

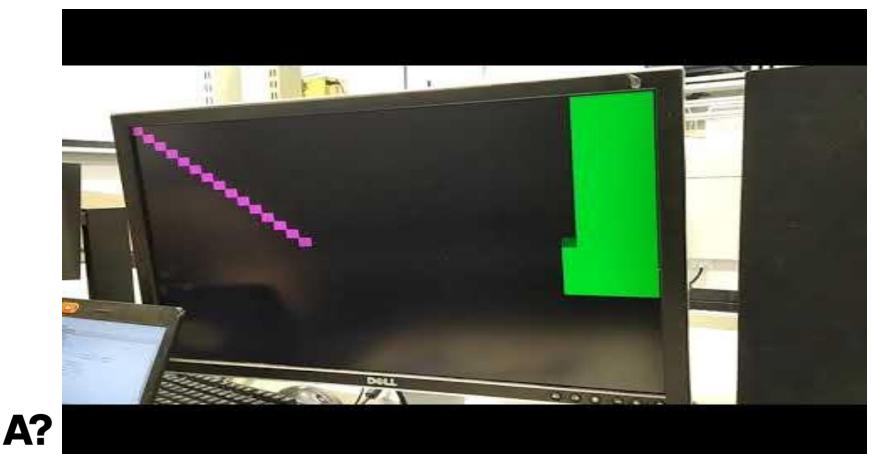

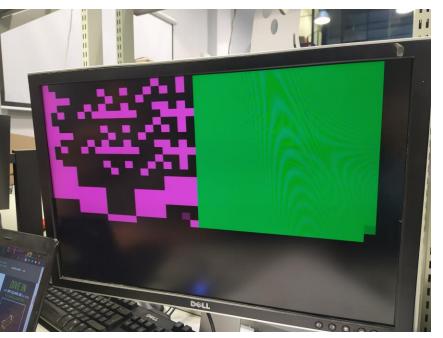

Trying out different ways of accessing pixels

Aalto-yliopisto Sähkötekniikan korkeakoulu

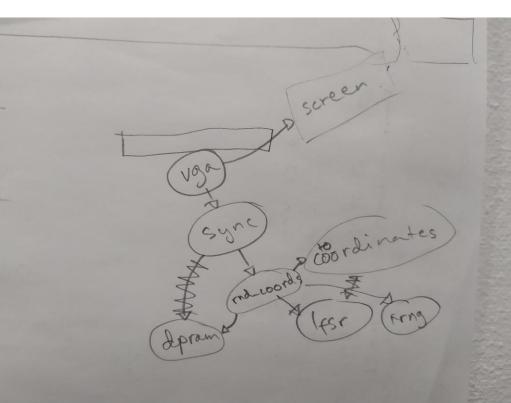

#### Towards a final design: draft of project hierarchy

## **Physical components**

## Current situation and final result

Under work:

Done:

VGA controller

**RAM** controller

**TRNG wrapper (not tested yet) PRNG** with wrapper **PMOD => VGA prototype**

Sketch of what the finished visualization should look like

Alto-vliopisto

**Finish Interpreter with** pi approximator and few pixel maps

Pixel size down

Nice casing

VHDL polishing

User manual

## **Comments & questions?**

#### Thank you for your attention!